Diskretes Transfergate für Hall-Signale

Ausgangslage

In einer bestehenden Schaltung wird ein Hall-Signal über einen BSS138 (N-Kanal MOSFET, SOT-23) geschaltet. Das funktioniert grundsätzlich, hat aber einen strukturellen Nachteil: Beim BSS138 ist das Substrat (Body) intern mit Source verbunden. In einer Analogschalter-Anwendung ist das ein Problem.

Warum der BSS138 hier nicht ideal ist

Bei einem MOSFET als Analogschalter fließt das Signal bidirektional zwischen Drain und Source. Source und Drain sind aus Sicht des Signals austauschbar -- aber der Body ist es nicht. Wenn Body fest an Source liegt:

- Body-Effekt: Sobald sich die Source-Spannung relativ zum Body verschiebt (also sobald ein Signal anliegt), steigt die Schwellenspannung V_th an. Das erhöht den R_on signalabhängig.

- Asymmetrischer R_on: Der Widerstand hängt von der Polarität des Signals ab -- nicht ideal für ein kleines, symmetrisches Hall-Signal.

- Substratdiode: Die parasitäre Body-Drain-Diode kann bei negativen Signalteilen leitend werden und das Signal verfälschen.

Für ein digitales Enable wäre das egal. Für ein analoges Messsignal im Millivolt-Bereich nicht.

Lösungsansatz: MOSFETs mit separatem Body

Die Lösung ist konzeptionell einfach: MOSFETs verwenden, bei denen der Body-Anschluss separat herausgeführt ist. Dann kann man den Body gezielt auf ein definiertes Potential legen (typisch: auf die niedrigste in der Schaltung vorkommende Spannung, oder auf ein eigenes Bias-Potential), um den Body-Effekt zu minimieren.

Kandidaten

SST210 (Linear Integrated Systems)

Bezugsquellen: Mouser · DigiKey · Datasheet (PDF)

| Parameter | Wert |

|---|---|

| Typ | N-Channel Lateral DMOS, Enhancement Mode |

| Package | TO-72 (4-Pin Metallgehäuse) |

| Anschlüsse | Gate, Drain, Source, Body (separat) |

| \(V_{(BR)DS}\) | 30 V |

| \(V_{GS(th)}\) | typ. 0.8 V (max 1.5 V) |

| \(r_{DS(on)}\) @ \(V_{GS}\) = 5 V | typ. 60 Ω (max 75 Ω) |

| \(r_{DS(on)}\) @ \(V_{GS}\) = 10 V | typ. 40 Ω (max 50 Ω) |

| \(r_{DS(on)}\) @ \(V_{GS}\) = 15 V | typ. 30 Ω |

| \(r_{DS(on)}\) @ \(V_{GS}\) = 25 V | typ. 24 Ω |

| \(t_{ON}\) | max 2 ns |

| \(C_{rss}\) | max 0.5 pF |

| \(I_D\) max | 50 mA |

Ein einzelner N-Kanal-FET mit separatem Bulk. Lateral DMOS-Konstruktion für niedrige Kapazitäten und ultra-schnelles Schalten. Kein interner Gate-Schutz (Zener) -- dafür niedrigere Gate-Leckströme und ±-Spannungsfähigkeit Gate-Substrat. Vorteil: einfach, ein Bauteil. Nachteil: als einzelner N-Kanal-FET hat er einen signalabhängigen \(r_{DS(on)}\). Der FET leitet nur solange \(V_{GS} > V_{th}\) gilt -- und \(V_{GS}\) ist die Differenz zwischen Gate und Source. Wenn das Signal am Source-Pin steigt (positive Halbwelle), sinkt \(V_{GS}\) und der FET wird hochohmiger. Bei \(V_S \geq V_G - V_{th}\) sperrt er ganz. Das begrenzt den nutzbaren Signalhub: er muss deutlich kleiner bleiben als \(V_G - V_{th}\). Genau das zeigen die Messungen weiter unten.

ALD1101ASAL + ALD1102PAL (Advanced Linear Devices)

Bezugsquellen ALD1101: Mouser · DigiKey Bezugsquellen ALD1102: Mouser · DigiKey

| Parameter | ALD1101ASAL | ALD1102PAL |

|---|---|---|

| Typ | N-Kanal (Dual) | P-Kanal (Dual) |

| Package | SOIC-8 | SOIC-8 |

| Anschlüsse je FET | Gate, Drain, Source, Body | Gate, Drain, Source, Body |

| V_th | typ. 0.5 V | typ. -0.5 V |

Beide ICs enthalten jeweils zwei gematchte MOSFETs mit separatem Body. Damit lässt sich ein vollständiges CMOS-Transfergate aufbauen: NMOS und PMOS parallel, mit komplementärer Gate-Ansteuerung.

Vorteile des CMOS-Transfergates:

- Konstanter R_on über den gesamten Signalbereich -- wo der NMOS hochohmig wird, übernimmt der PMOS und umgekehrt

- Rail-to-Rail-fähig -- das Signal kann den gesamten Bereich zwischen den Versorgungsschienen durchlaufen

- Niedrige Schwellenspannung (typ. 0.5 V) -- besonders hilfreich bei niedrigen Versorgungsspannungen

- Zweiter FET als Reserve -- die Duals haben jeweils zwei FETs, der zweite kann für einen zweiten Kanal oder als Guard verwendet werden

Schaltungskonzept

Variante 1: SST210 einzeln

Hall-Signal ──── Drain ┐

│ SST210

Source ────┘──── Ausgang

│

Body → V_bias (z.B. GND oder negative Hilfsspannung)

Gate ← Enable-Signal (High = an, Low = aus)

Einfach, aber nur für Signale innerhalb V_GS - V_th brauchbar.

Variante 2: CMOS-Transfergate (ALD1101 + ALD1102)

┌──── ALD1101 (NMOS) ────┐

Hall-Signal ────────┤ ├──── Ausgang

└──── ALD1102 (PMOS) ────┘

Enable ──────────── Gate NMOS

Enable (invertiert) ── Gate PMOS

Body NMOS → GND (oder V_SS)

Body PMOS → V_DD

Die komplementäre Ansteuerung sorgt dafür, dass bei Enable=High der NMOS und der PMOS gleichzeitig leiten. Der resultierende R_on ist über den Signalbereich nahezu konstant.

Handlungsempfehlungen

1. Body-Bias richtig wählen

Der ganze Sinn der Übung ist der separate Body -- also muss der auch sinnvoll beschaltet werden:

- NMOS-Body auf das negativste Potential im Signalpfad legen (typisch GND oder V_SS). Niemals positiver als Source, sonst leitet die Body-Diode.

- PMOS-Body auf das positivste Potential (V_DD). Niemals negativer als Source.

- Wenn das Hall-Signal um 0 V schwingt und keine negative Versorgung vorhanden ist: Body des NMOS an GND, aber bewusst sein dass der Body-Effekt bei negativen Signalteilen zuschlägt. Besser: symmetrische Versorgung verwenden (z.B. +/-5 V).

2. Gate-Ansteuerung sauber halten

- Für das CMOS-Gate brauchst du ein Enable-Signal und dessen Invertierung. Ein einfacher Inverter (z.B. ein Gate aus einem 74HC04) reicht.

- Flanken synchron halten -- wenn NMOS und PMOS nicht gleichzeitig schalten, gibt's kurze Momente wo keiner leitet (Break-before-Make) oder beide leiten. Für langsame Schaltvorgänge (kein kHz-Betrieb) ist das unkritisch.

- Gate-Vorwiderstände sind bei diesen FETs unnötig -- die Gate-Kapazität ist winzig.

3. Charge Injection beachten

Beim Schalten koppelt die Gate-Drain-Kapazität (C_GD) einen kleinen Ladungsstoß ins Signal. Bei Millivolt-Hall-Signalen kann das relevant sein:

- Kompensation durch CMOS-Gate: NMOS und PMOS injizieren Ladung mit entgegengesetztem Vorzeichen -- im Idealfall heben sie sich teilweise auf.

- Langsamere Schaltflanken reduzieren den Spitzenstrom der Charge Injection.

- Sample-and-Hold nach dem Gate kann den Effekt eliminieren -- das Signal wird erst abgetastet nachdem sich die Störung beruhigt hat.

4. Leckströme im Aus-Zustand

Im ausgeschalteten Zustand fließt ein kleiner Leckstrom durch den FET. Bei den ALD-Teilen typisch im pA-Bereich -- für Hall-Signale im mV-Bereich an niederohmigen Quellen komplett vernachlässigbar. Aber: bei hochohmiger Signalquelle oder langen Haltezeiten an einem Kondensator wirds relevant.

Messtechnik

Für die Charakterisierung brauchen wir drei Dinge: R_on über den Signalbereich, Verzerrung (THD), und das Schaltverhalten.

R_on vs. Signalspannung

Die wichtigste Messung. Zeigt direkt, ob der Body-Effekt eliminiert ist.

Aufbau: Bekannten DC-Pegel am Eingang anlegen (Labornetzteil oder DAC, in kleinen Schritten von z.B. -1 V bis +1 V), Gate auf High, Ausgangsspannung über bekannter Last messen. R_on ergibt sich aus der Differenz.

Tools:

| Tool | Wozu |

|---|---|

| Sourcemeter (z.B. Keithley 2400 / 2450) | Ideales Gerät -- kann gleichzeitig Strom forcen und Spannung messen (4-Wire). Gibt direkt R_on. |

| Multimeter 6.5 Digit (z.B. Keithley DMM6500) | Für die Spannungsmessung am Ausgang. Bei kleinen Signalen brauchst du die Auflösung. |

| Labornetzteil mit feiner Einstellung | Für den Signalpegel am Eingang. Alternativ: DAC-Board (z.B. MCP4922 am ESP32). |

Wenn kein Sourcemeter vorhanden: Einen bekannten Strom (z.B. 1 mA über einen Präzisionswiderstand) durch den FET schicken und die Drain-Source-Spannung mit dem Multimeter messen. R_on = V_DS / I.

THD / Klirrfaktor

Zeigt ob das Gate das Signal verzerrt.

Aufbau: Sinus (z.B. 1 kHz, einige mV bis einige hundert mV) am Eingang, Ausgang am PicoScope messen.

Tools:

| Tool | Wozu |

|---|---|

| Funktionsgenerator | Sauberer Sinus als Testsignal. Wichtig: der Generator selbst muss klirrarm sein (< -80 dB THD), sonst misst man den Generator statt das Gate. |

| PicoScope 3406D MSO | 12-14 Bit Auflösung -- damit sind THD-Messungen bis ca. -80 dB realistisch. Die PicoScope-Software hat eingebaute FFT und Spektrumansicht. Deutlich besser als 8-Bit-Scopes. |

| PicoScope 3406D MSO (Differenzeingänge) | Ideal für die Hall-Signal-Messung: direkt über dem Gate differenziell messen, keine Masseschleife, kein Ground-Loop-Rauschen. |

Die PicoScope-Software kann direkt FFT und Spektralanalyse -- kein externer Workaround nötig. Alternativ die Daten als CSV exportieren und mit Python (numpy.fft) auswerten, wenn man mehr Kontrolle will.

Schaltverhalten und Charge Injection

Aufbau: Gate mit Rechteck ansteuern, Ausgangsspannung am Scope beobachten. Signal am Eingang auf DC legen (z.B. 0 V). Jeder Spike am Ausgang ist Charge Injection.

Tools:

| Tool | Wozu |

|---|---|

| PicoScope 3406D MSO | Charge-Injection-Spikes sind kurz (ns-Bereich). Das 3406D MSO hat genug Bandbreite dafür. Gute Tastköpfe verwenden, Massefeder statt Krokodilklemme. |

| PicoScope 3406D MSO | Differenzmessung direkt über Drain-Source -- sieht die Injection ohne Ground-Loop-Artefakte. |

| Signalgenerator / GPIO | Rechteck-Enable-Signal. Frequenz ist egal (1 kHz reicht), wichtig sind die Flanken. |

Vorhandenes Equipment

| Gerät | Einsatz in diesem Projekt |

|---|---|

| PicoScope 3406D MSO | R_on-Sweep (DC-Pegel variieren, V_DS messen), THD via FFT, Charge Injection |

| PicoScope 3406D MSO | Differenzmessung am Gate-Ausgang, Hall-Signal im realen Aufbau ohne Masseschleifen |

| Multimeter | Statische R_on-Messung zur Gegenprüfung, Versorgungsspannungen kontrollieren |

Damit sind alle Messungen abgedeckt. Für die finale Messung am echten Hall-Sensor (Signal im mV-Bereich) wäre ein Scope mit Differenzeingängen ideal, um Ground-Loop-Artefakte zu vermeiden.

Erste Messungen: SST210

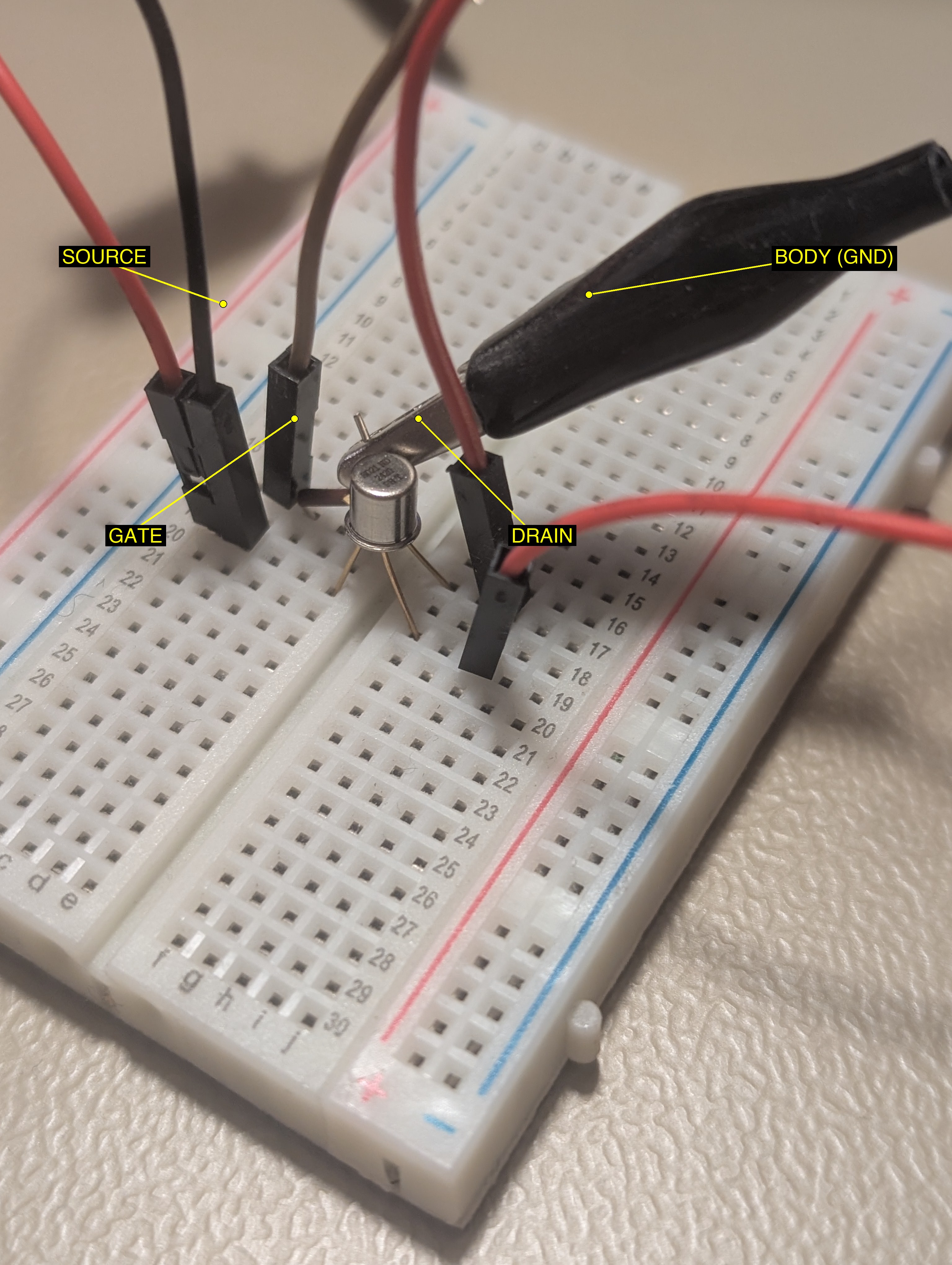

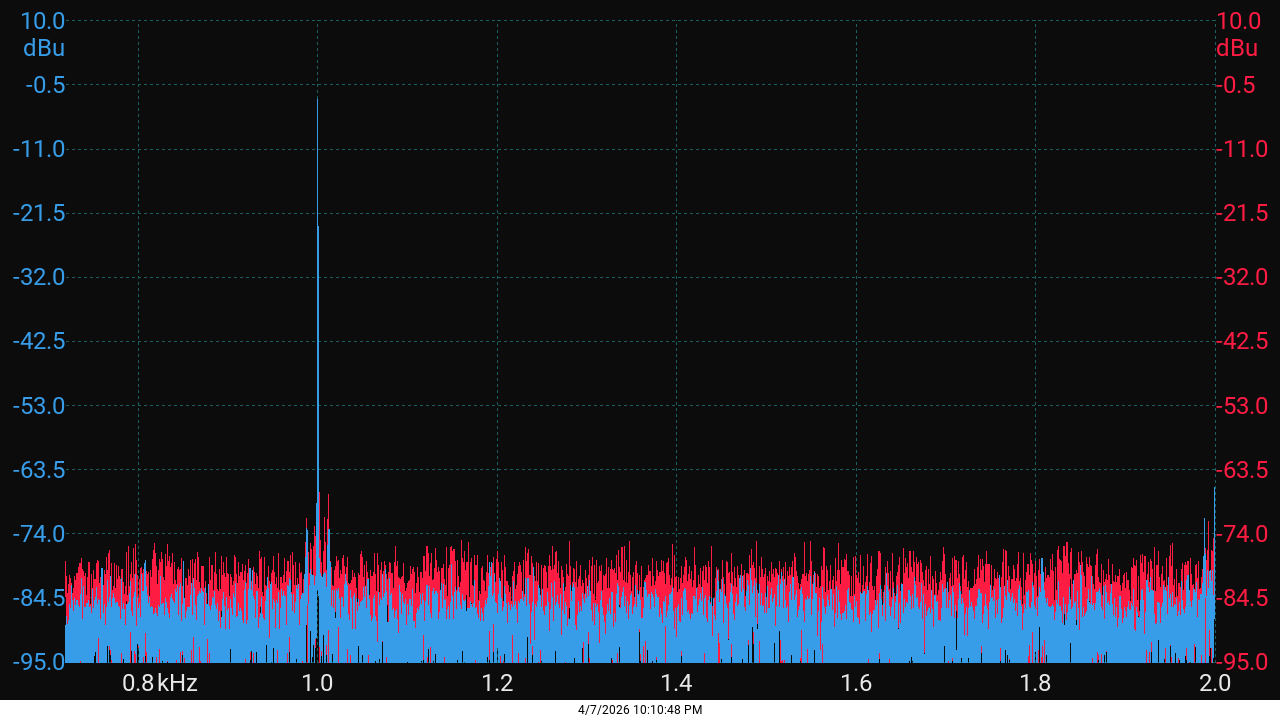

Testaufbau mit dem PicoScope 3406D MSO -- das Gerät dient gleichzeitig als Signalgenerator (1 kHz Sinus), Oszilloskop (Zeitbereich) und Spektrumanalysator (FFT):

- SST210 auf Breadboard, Body auf GND

- Eingangssignal: PicoScope AWG-Ausgang, 1 kHz Sinus, Center 1 V, Amplitude ±0.8 V (also 0.2 V bis 1.8 V)

- Gate-Spannung: DC vom Labornetzteil, variiert von 2 V bis 4 V

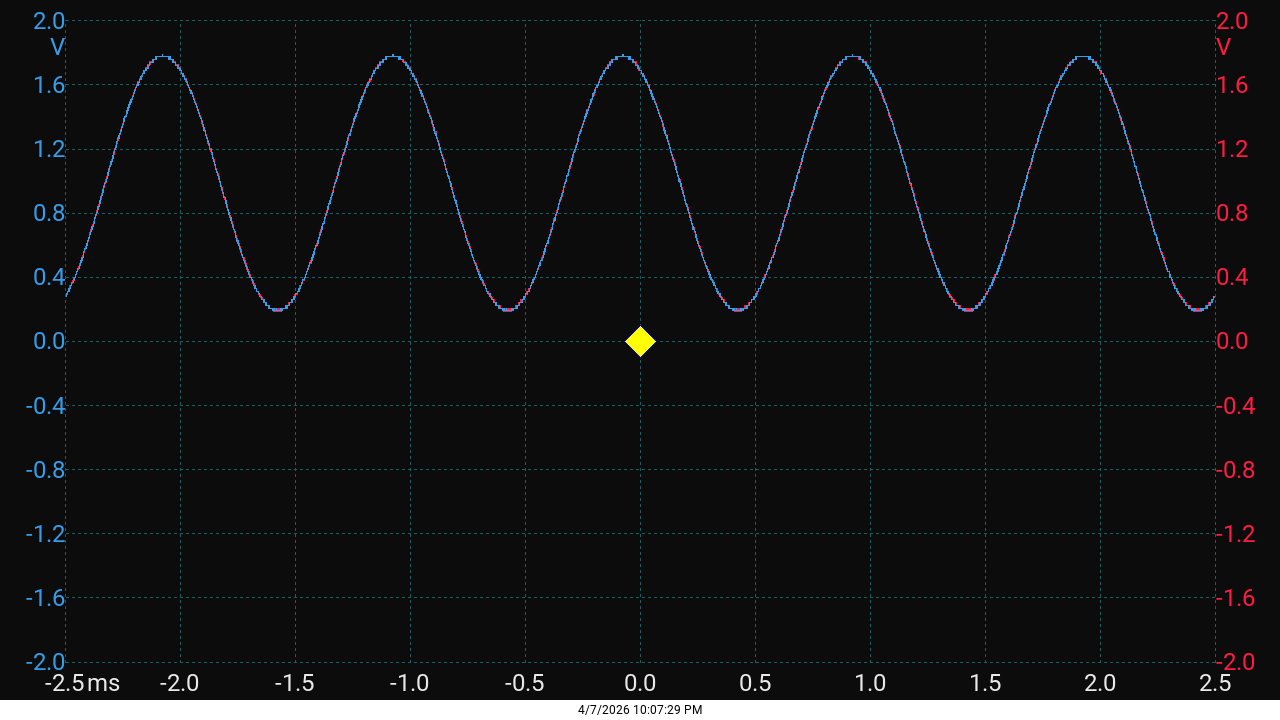

- Blau: Ausgangssignal (Drain), Rot: Eingangssignal (Source)

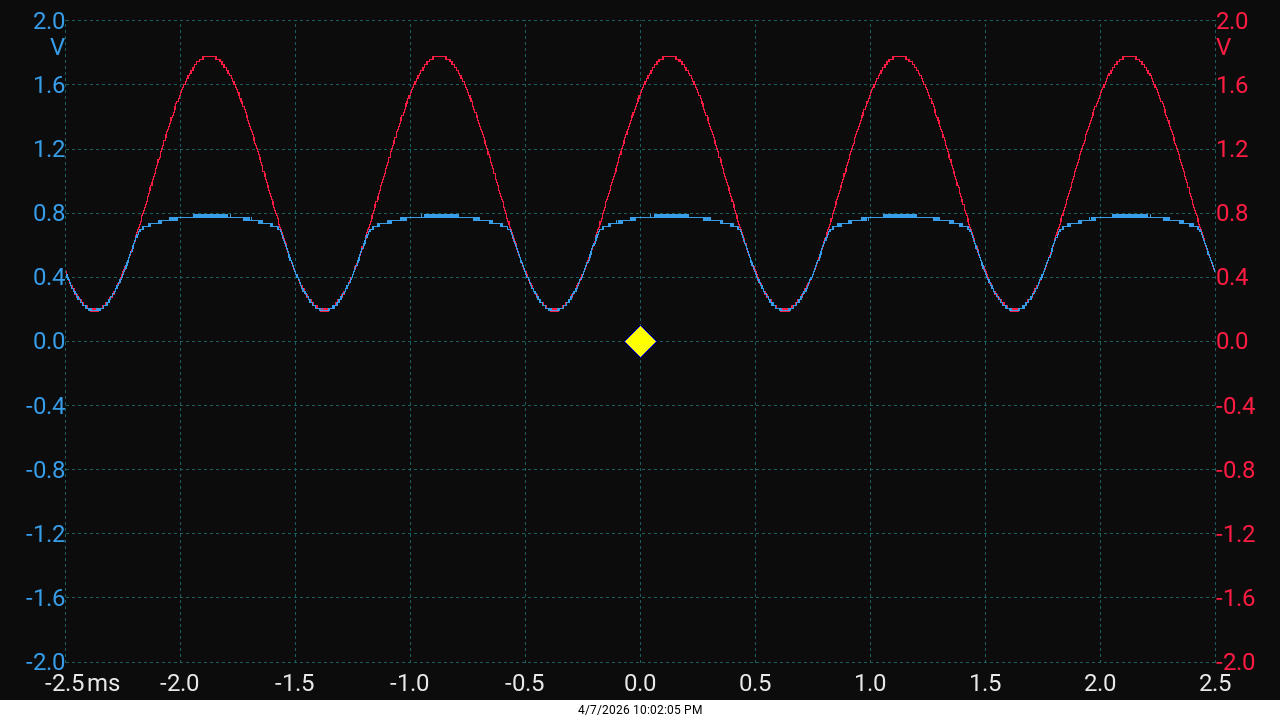

Gate = 2 V

Bei \(V_{GS}\) = 2 V ist der FET nur knapp über der Schwelle (\(V_{th}\) ≈ 0.8 V). Der \(r_{DS(on)}\) ist hoch und stark signalabhängig -- bei den positiven Spitzen (Source nah an Gate-Potential) steigt die effektive Schwellenspannung durch den verringerten \(V_{GS}\), und der FET sperrt. Das Signal wird oben abgeschnitten.

Gate = 3 V

Deutlich besser. Mehr Gate-Übersteuerung, der FET bleibt auch bei den positiven Signalspitzen leitend. Aber die Spitzen sind immer noch leicht komprimiert -- \(r_{DS(on)}\) ist bei den Maxima höher als bei den Minima.

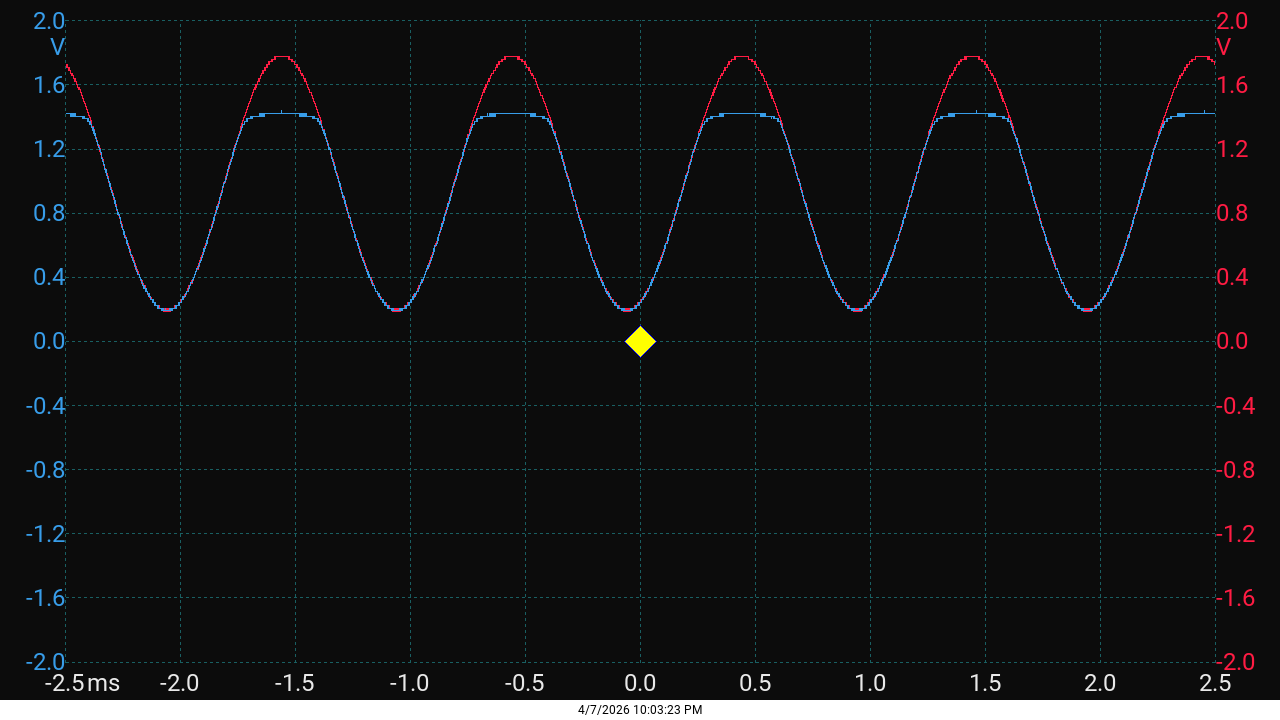

Gate = 4 V

Saubere Übertragung. Mit \(V_{GS}\) = 4 V am oberen Signalpeak (\(V_S\) = 1.8 V) bleibt immer noch \(V_{GS} - V_S\) = 2.2 V Übersteuerung -- genug für einen niedrigen, halbwegs konstanten \(r_{DS(on)}\).

FFT bei Gate = 4 V

Die FFT bestätigt: Grundwelle bei 1 kHz dominiert, Harmonische liegen im Rauschboden (ca. -60 dB und darunter). Für einen einzelnen N-Kanal-FET ohne komplementären P-Kanal ein gutes Ergebnis.

Fazit der ersten Messung

Der SST210 funktioniert als Analogschalter, aber man sieht deutlich die Grenzen eines einzelnen N-Kanal-FETs: die Gate-Übersteuerung muss deutlich größer sein als der Signalhub. Für ein Rail-to-Rail-fähiges Gate mit konstantem \(r_{DS(on)}\) braucht es den CMOS-Ansatz (ALD1101 + ALD1102).

Nächste Schritte

- [ ] Fotos vom Aufbau einfügen

- [ ] ALD1101/ALD1102 bestellen und CMOS-Transfergate aufbauen

- [ ] \(r_{DS(on)}\) vs. Signalspannung messen (DC-Sweep, alle Varianten vergleichen)

- [ ] Charge Injection am Scope charakterisieren

- [ ] Hall-Signal im realen Aufbau testen